1,文件夹管理

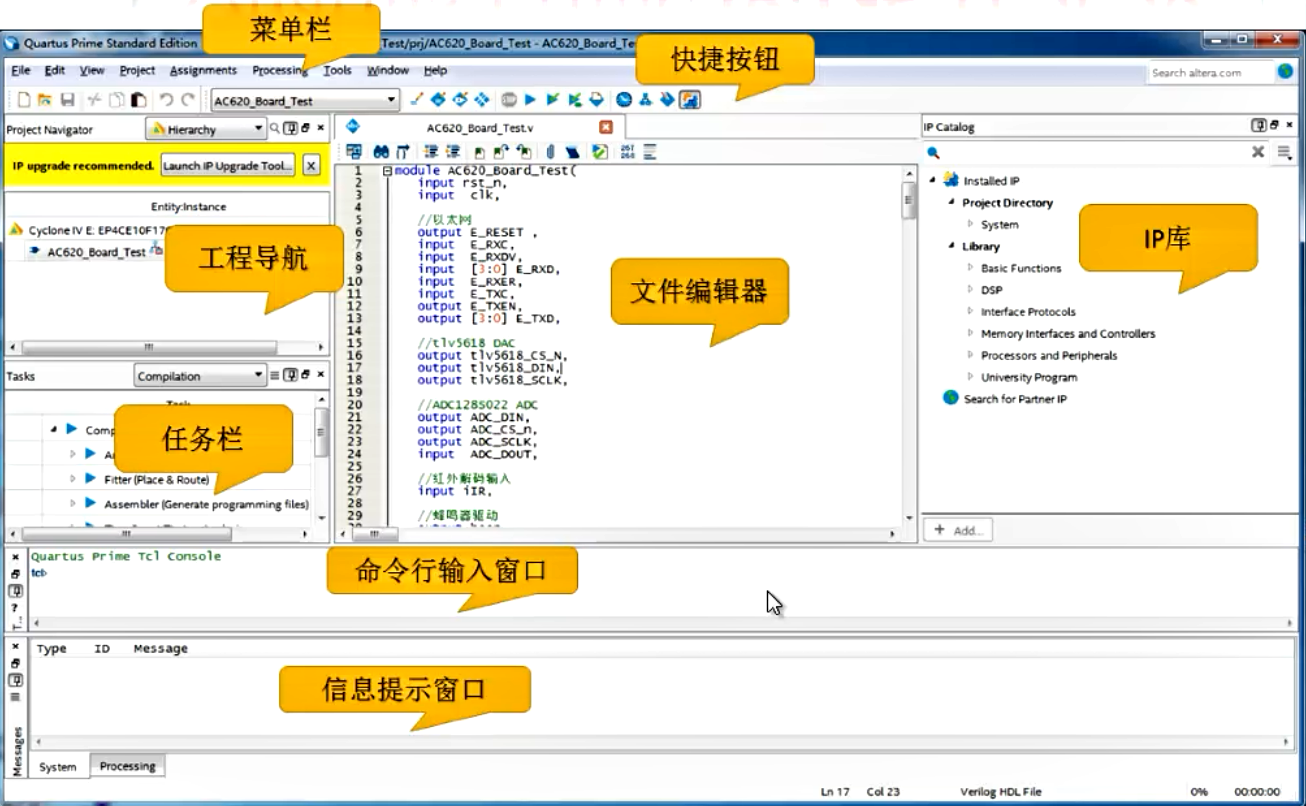

2,软件介绍

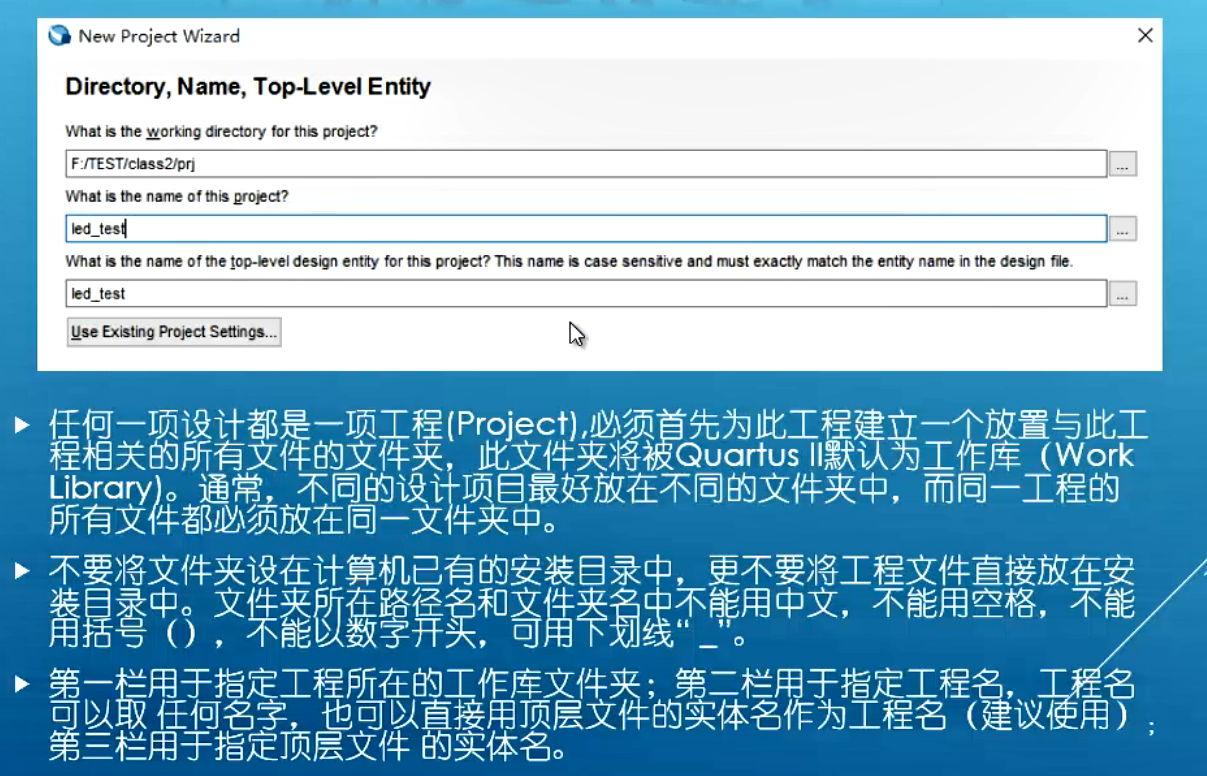

3,创建工程

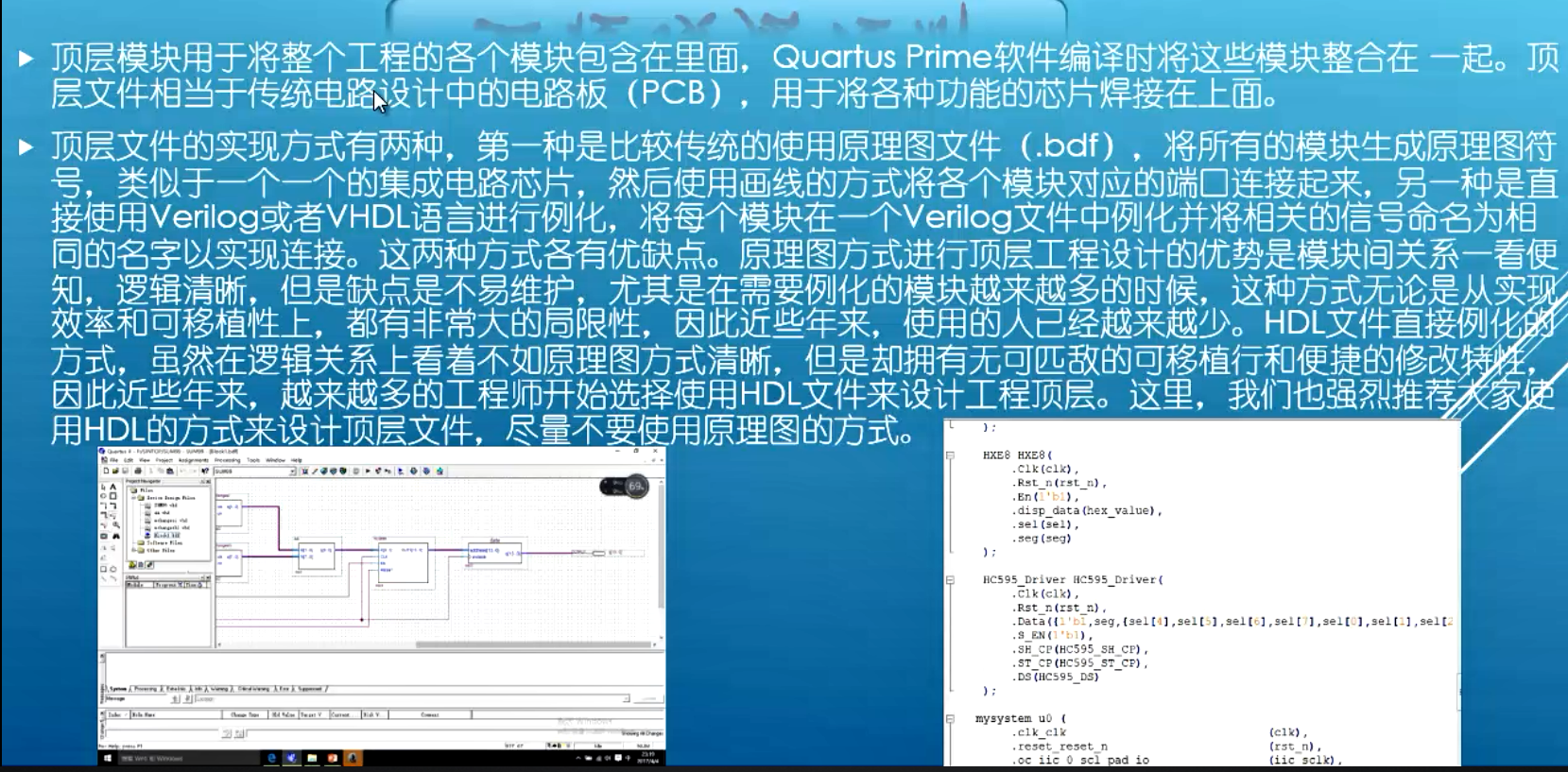

4,设计流程

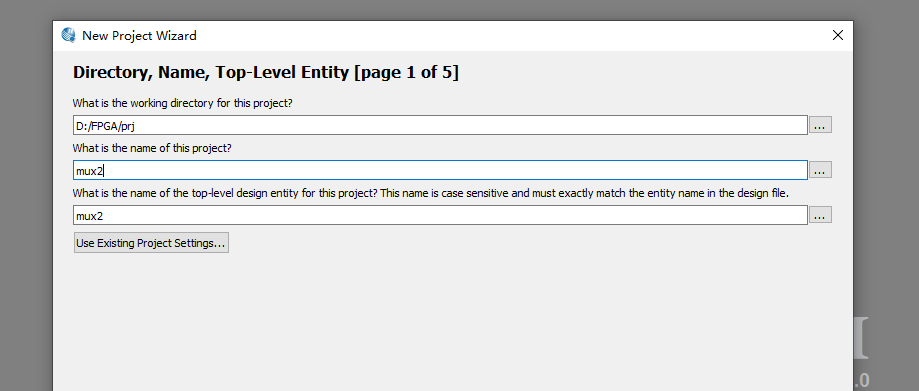

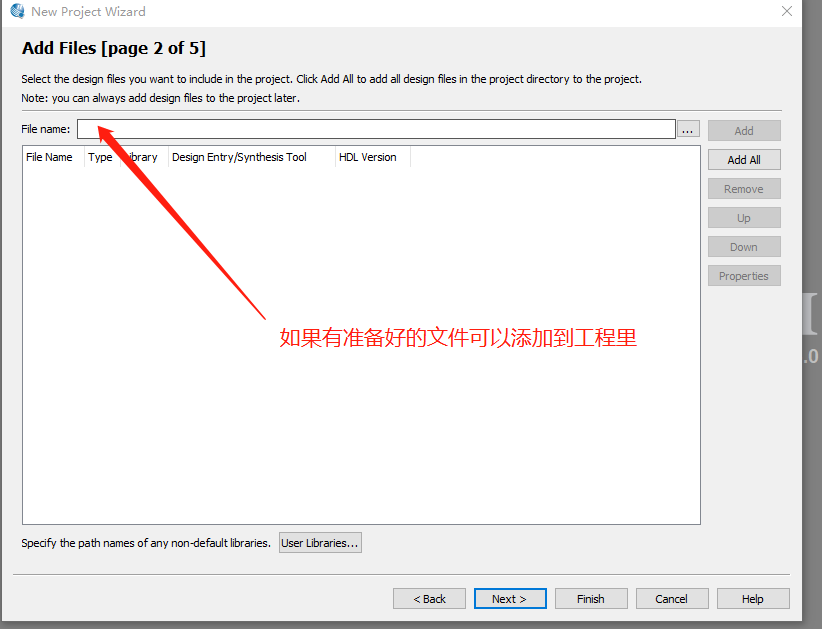

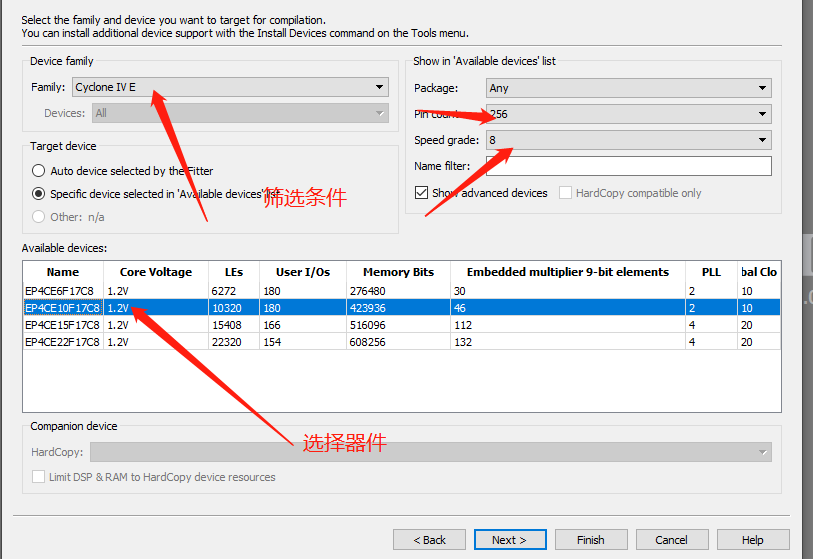

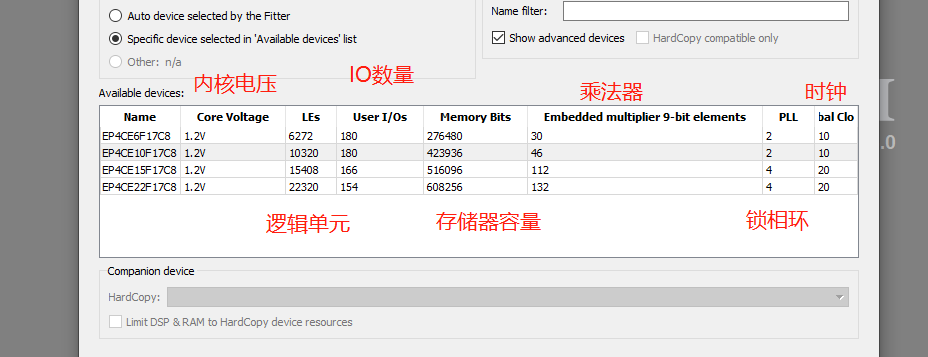

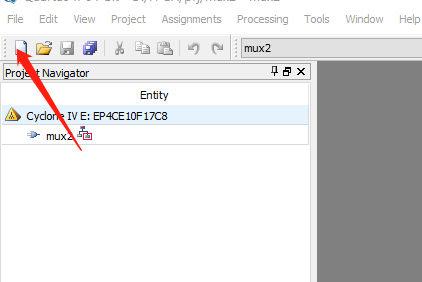

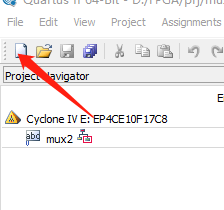

4.1新建工程

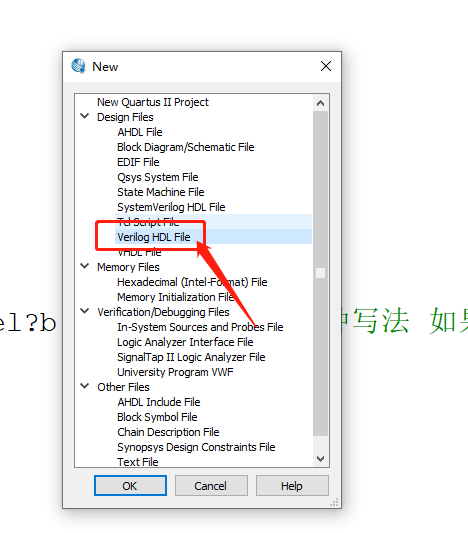

4.2新建Verilog HDL文件

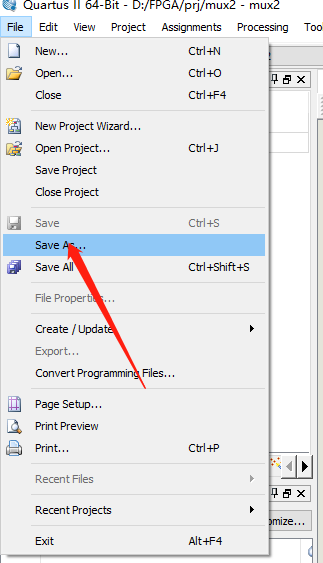

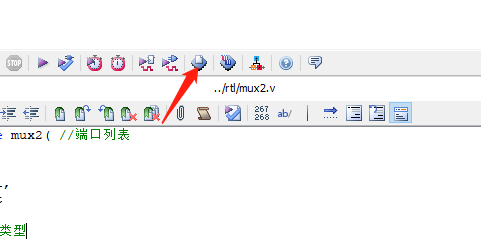

4.3保存到rtl目录

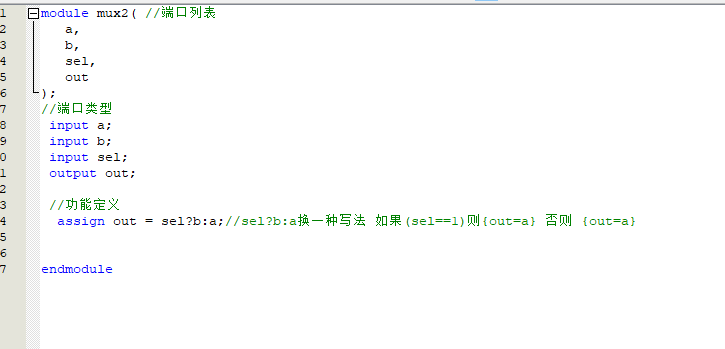

4.4 代码

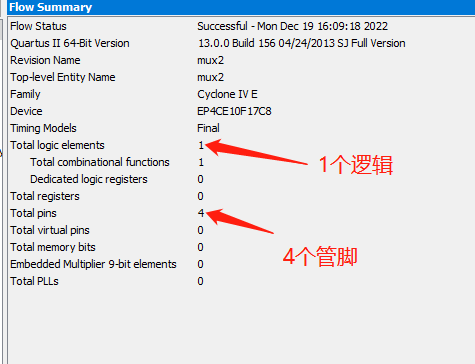

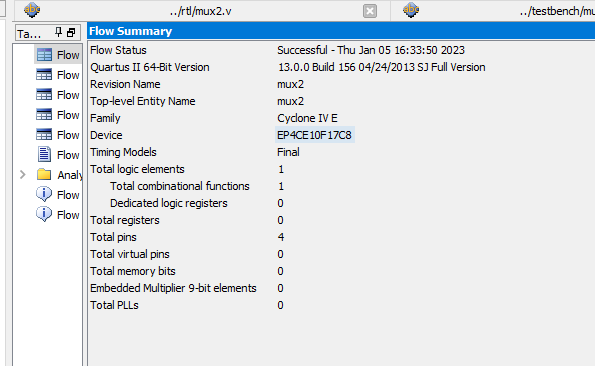

4.5分析和综合CTRL+K

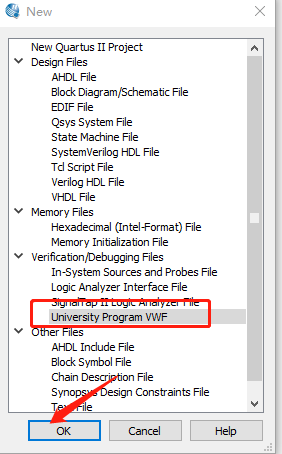

4.6验证仿真

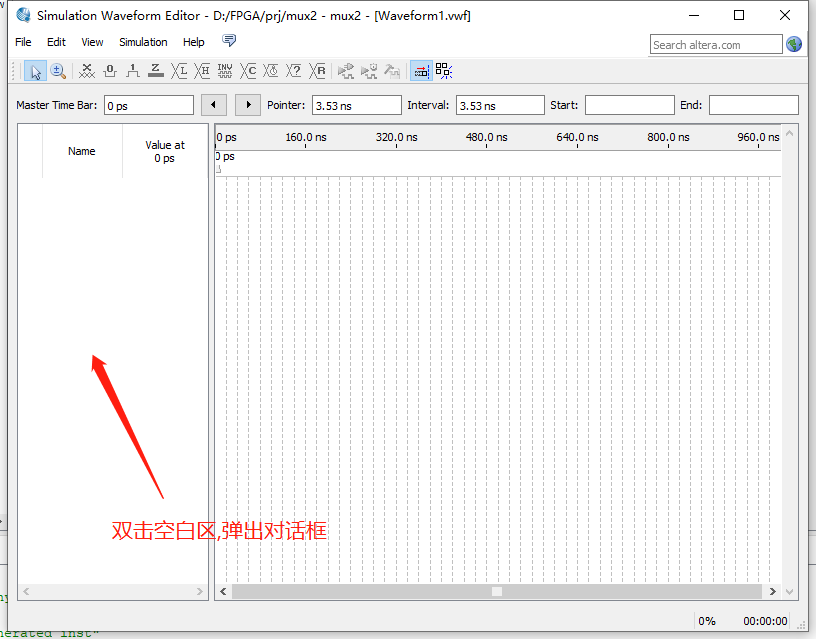

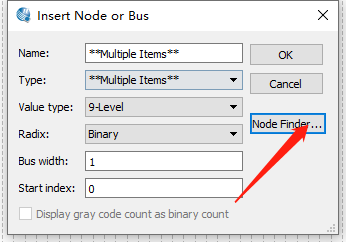

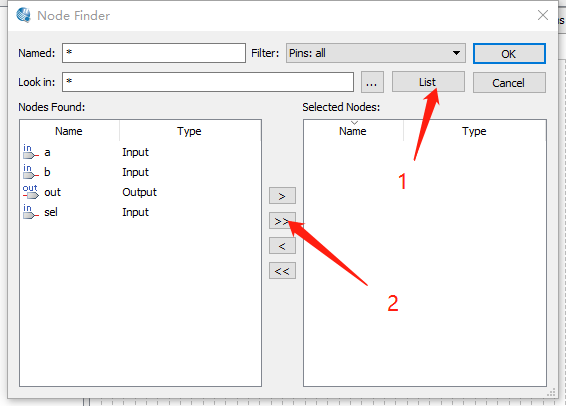

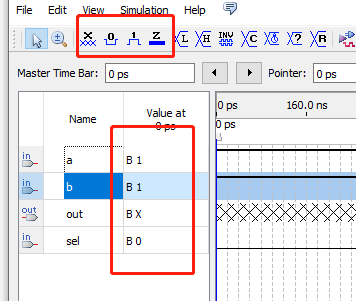

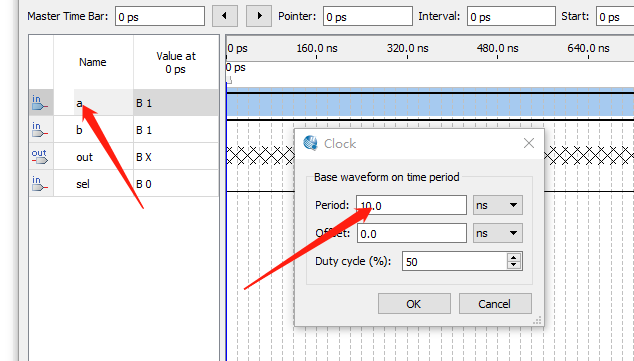

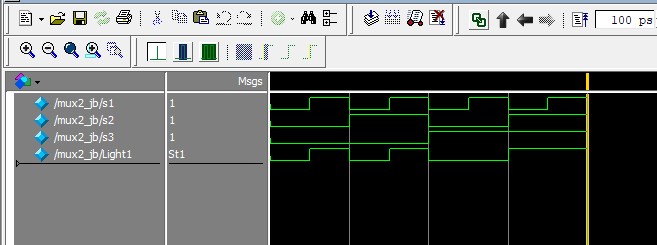

设置波形

设置波形

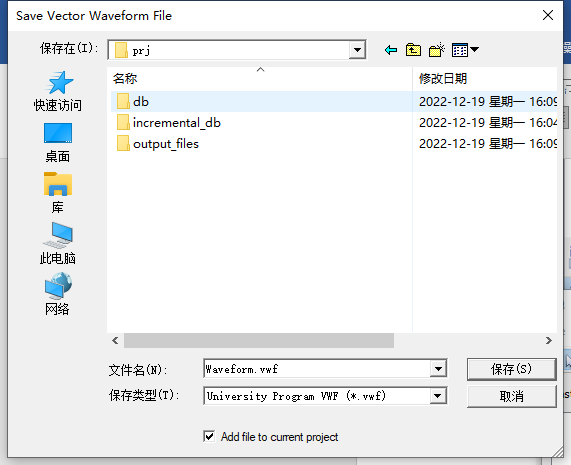

4.7保存

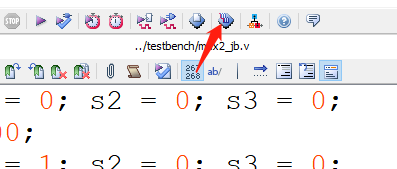

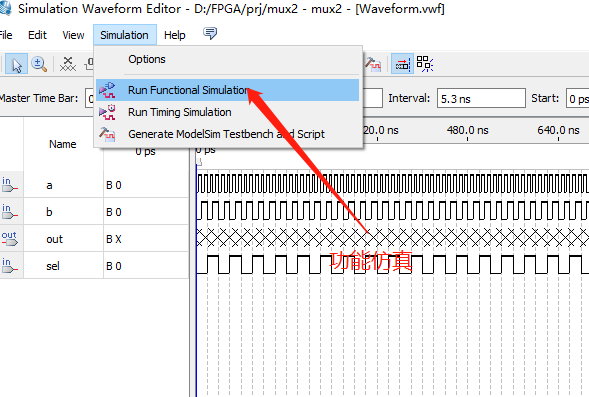

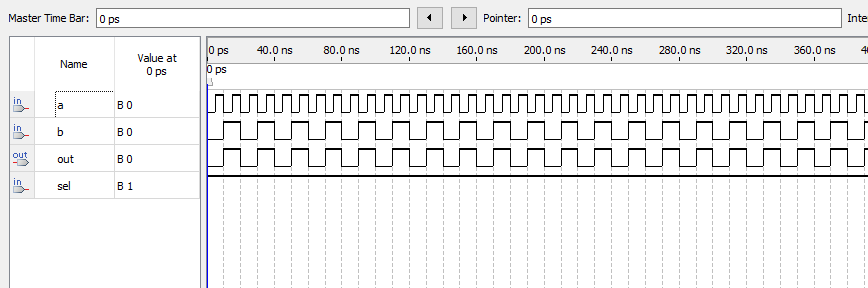

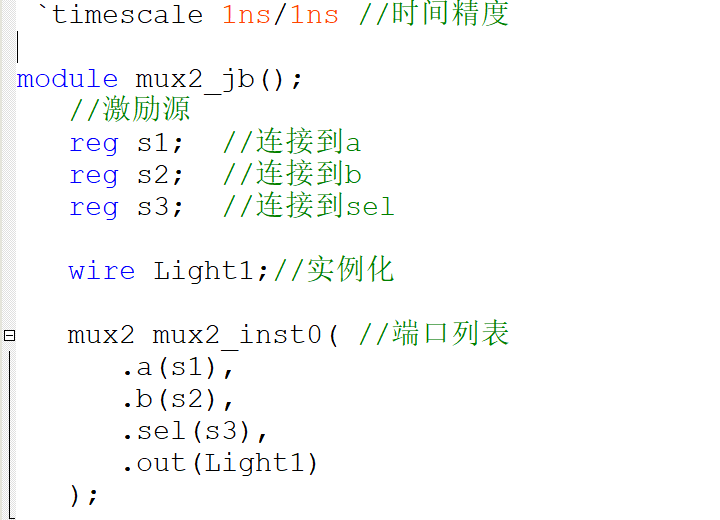

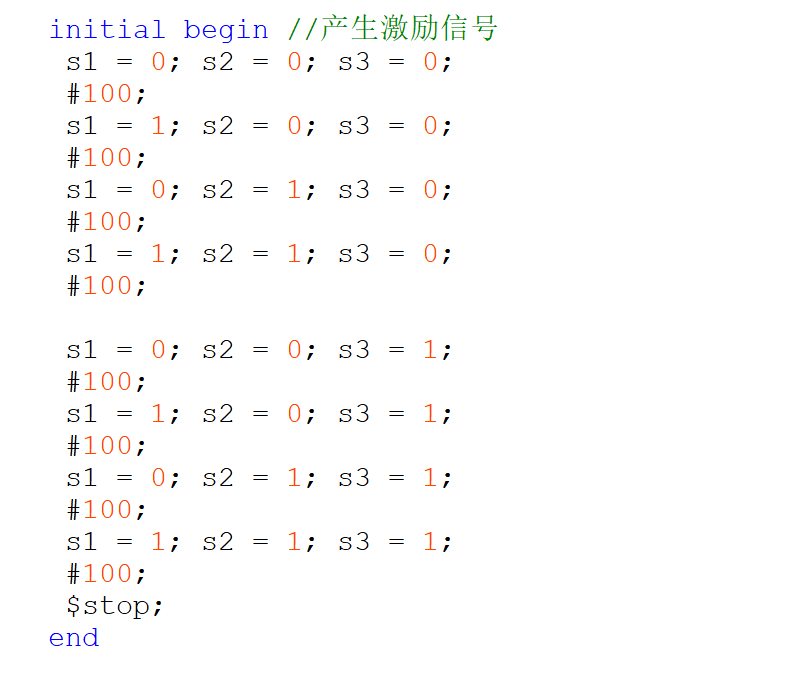

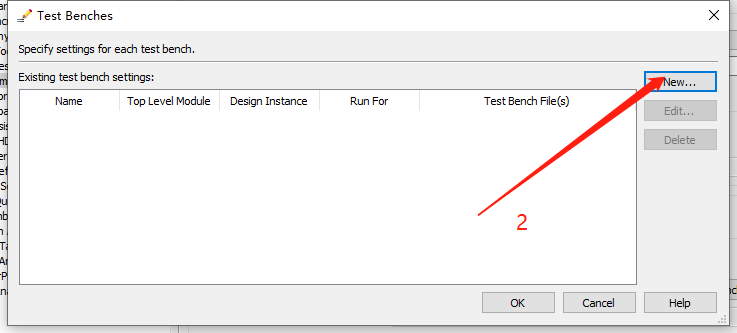

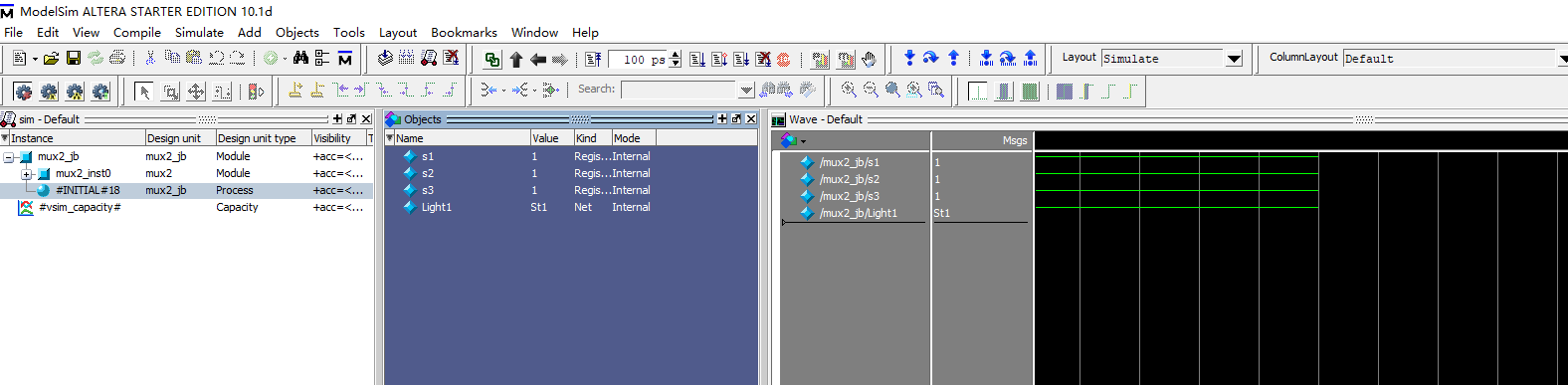

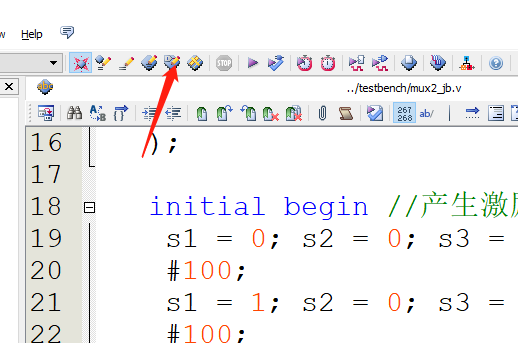

5,仿真,上面是波形仿真,用的较少,一般用modelsim,但是需要编写测试脚本

编写测试脚本和写程序一样

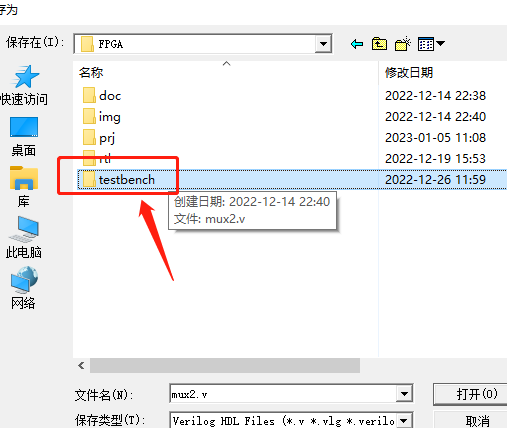

5.1保存

5.2CTRL+K运行分析和综合

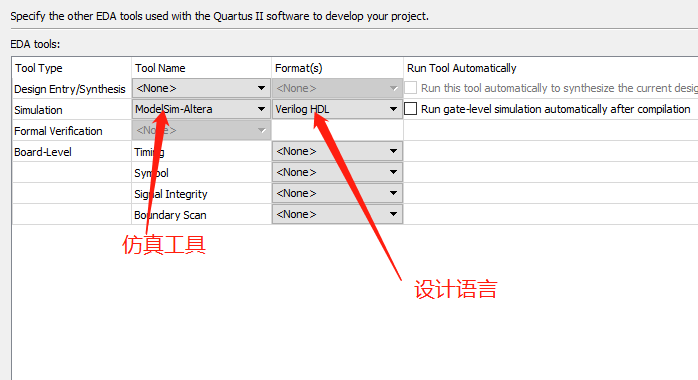

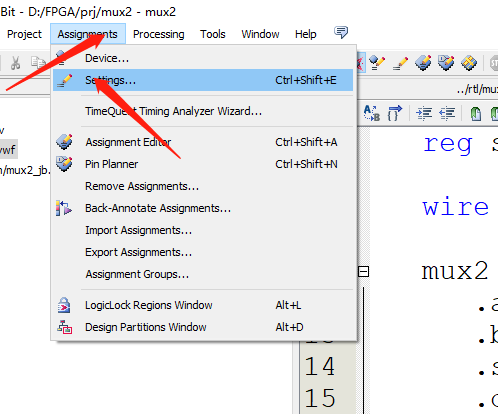

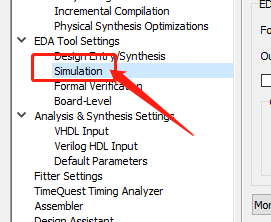

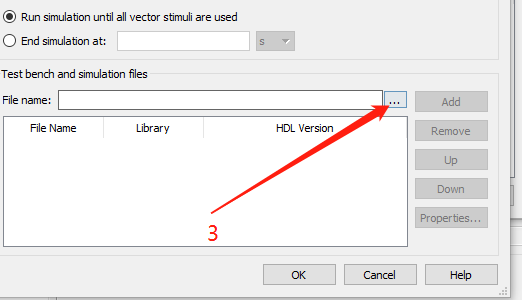

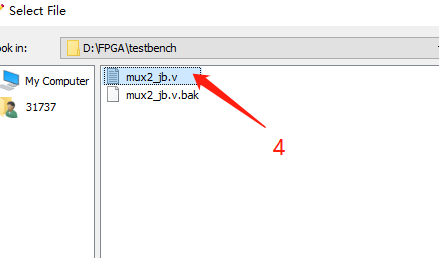

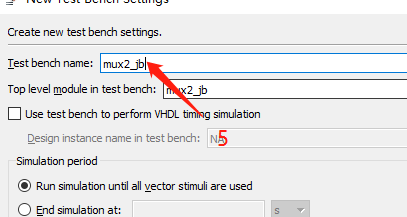

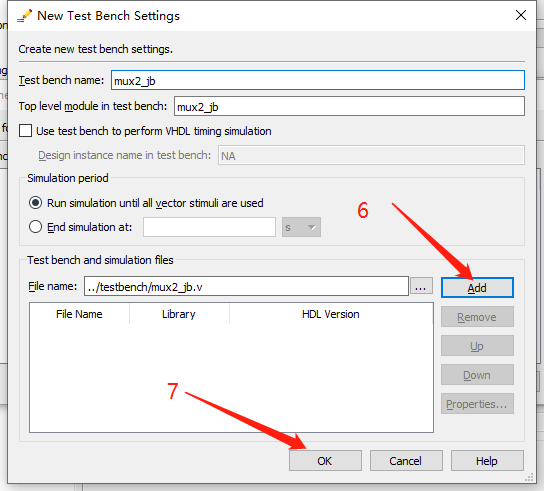

6,设置nativelink(联合仿真)

设置完成.

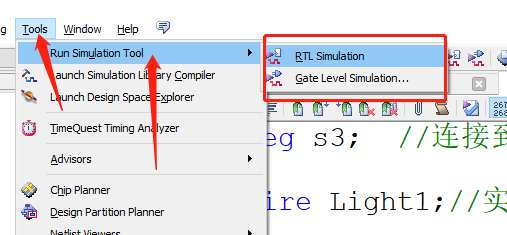

6.1运行

RTL是理想仿真,即功能仿真;Gate是逻辑延迟仿真.各种运算会占用时间.

6.2开启仿真,功能仿真又叫前仿真

7,门级仿真

对工程全编译

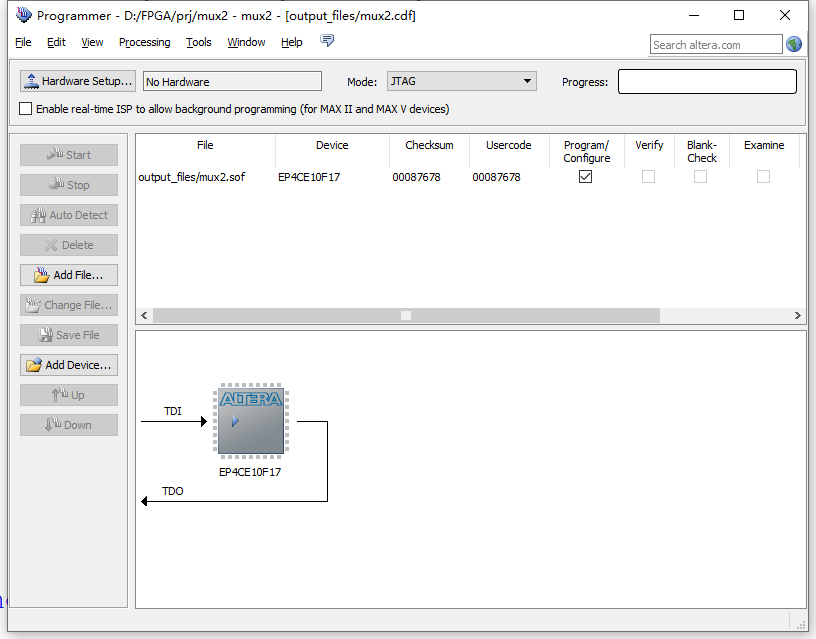

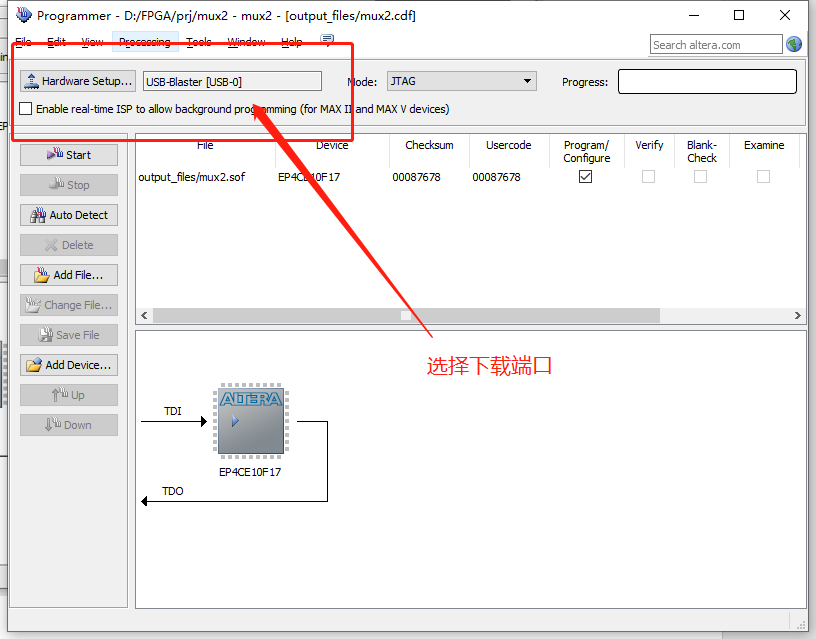

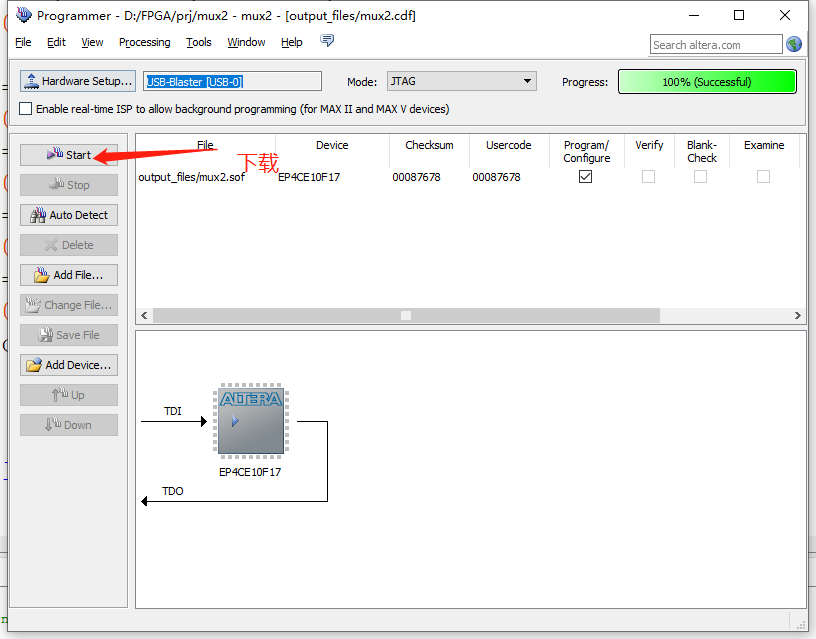

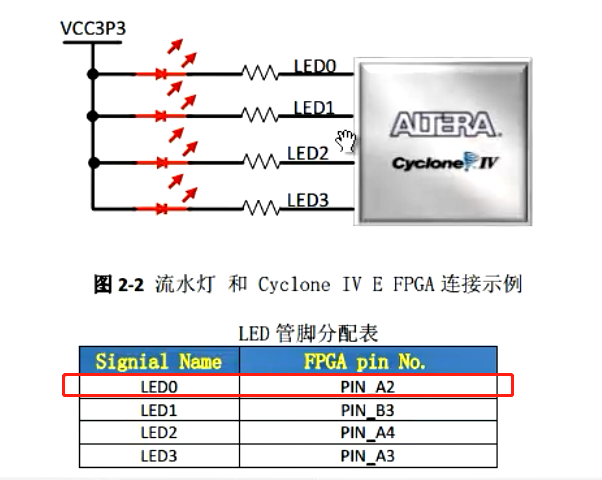

8,下载到电路板上

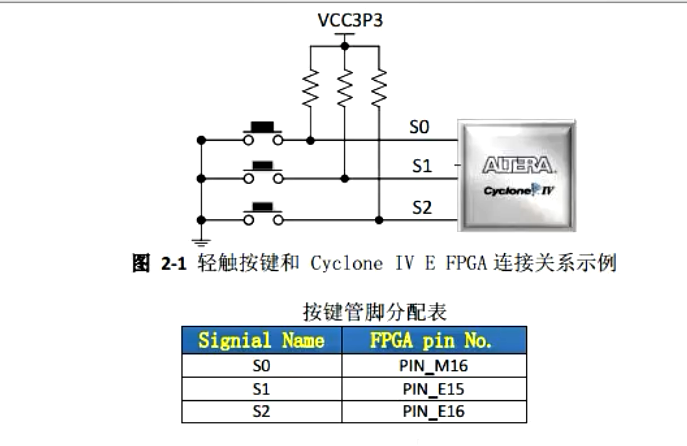

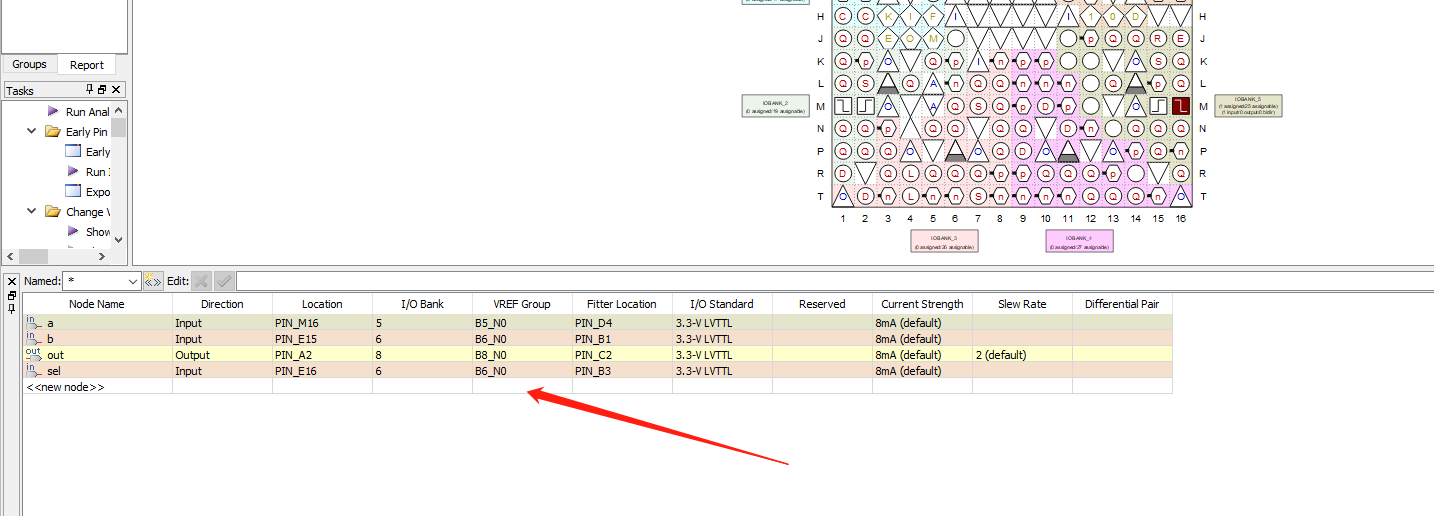

8.1,先配置引脚

LED选用A2脚,

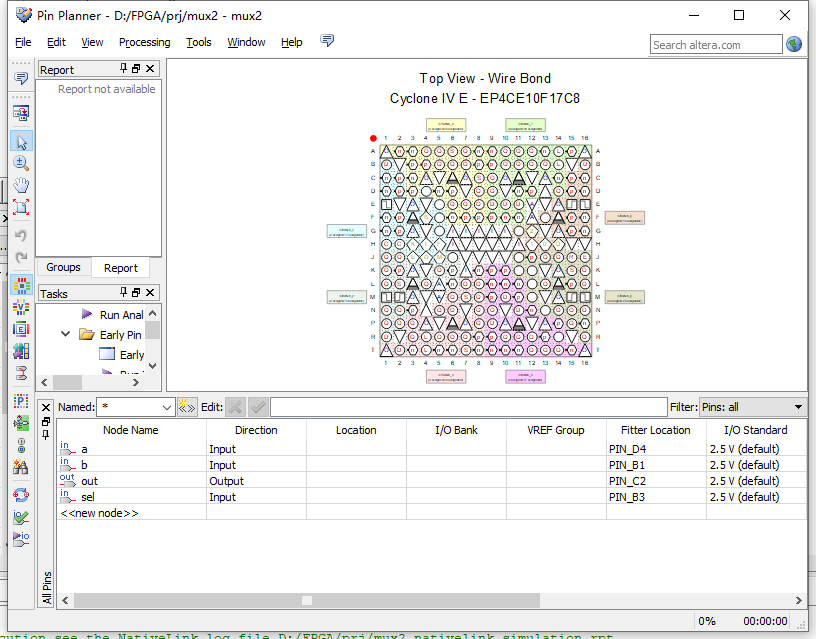

8.2打开引脚分配

8.3添加引脚

分配引脚后全编译,然后点击programmer